Press release - San Francisco, California, July 13, 2010

ASML Holding NV (ASML) today at SEMICON West announces broad customer adoption of holistic lithography products which optimize semiconductor scanner performance and provide a faster start to chip production. Of ASML's leading-edge scanners, 100% are now sold with one or more holistic lithography components. Semiconductor manufacturers face increasingly smaller margins of error as they shrink chip features. Holistic lithography provides a way to shrink within these margins to continue Moore's Law.

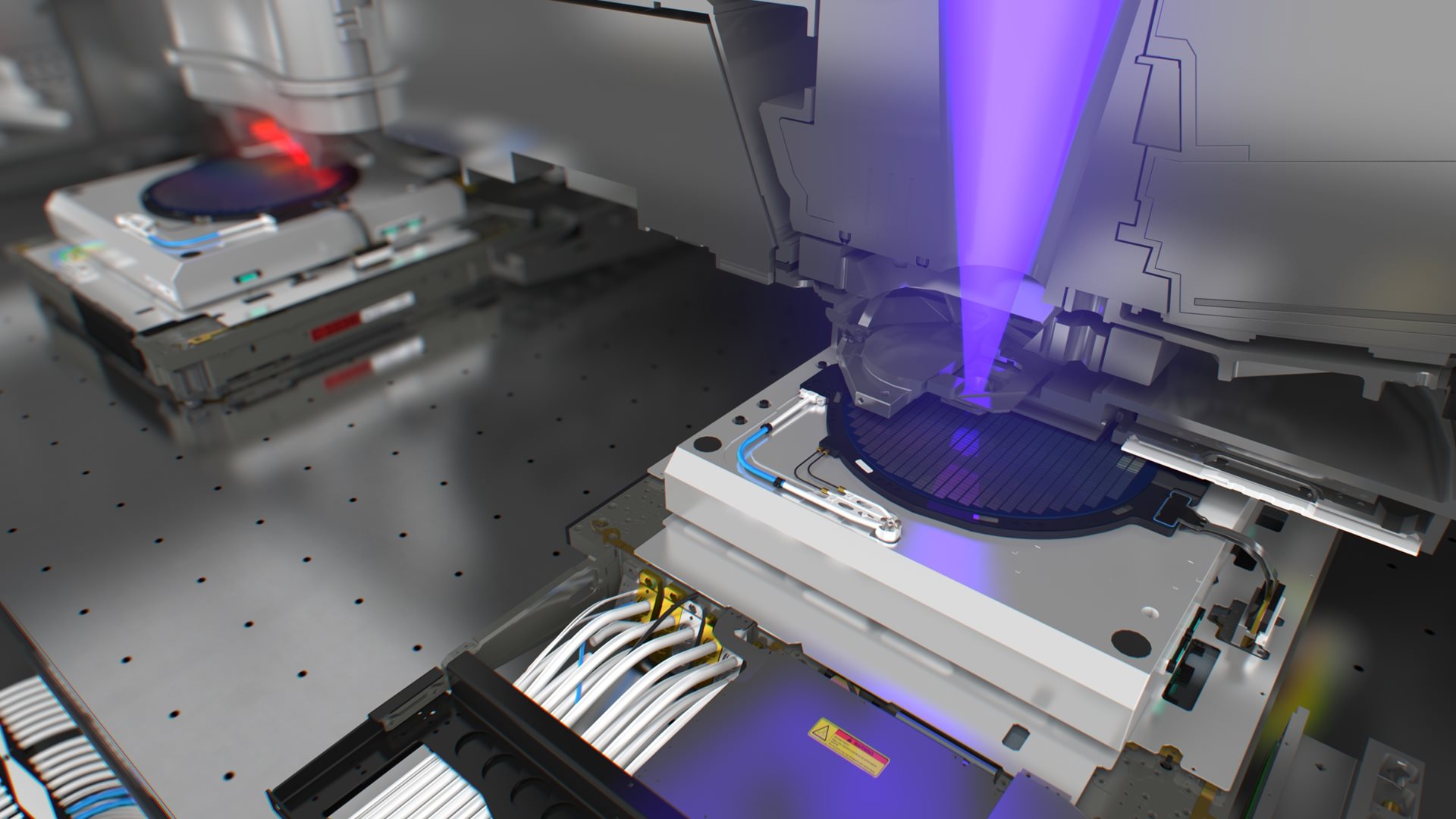

Introduced a year ago at SEMICON West 2009, ASML's holistic lithography suite of products enable continued shrink and provide customers with higher yield, sooner. Holistic lithography integrates computational lithography, wafer lithography and process control to optimize production tolerances and reduce 'time to money' for chipmakers. All of our customers have adopted multiple products from the holistic product portfolio into research and development (R&D) as well as volume manufacturing. Products such as Source Mask Optimization (SMO), FlexRay, LithoTuner, Baseliner and YieldStar are in use worldwide.

ASML also offers holistic lithography as an integrated package called Eclipse, which is tailored to a specific customer, node and application, and which enables chipmakers to squeeze every last bit of performance out of the chipmaking process and to enter volume production at the earliest possible time. A significant number of ASML's advanced customers have adopted an integrated Eclipse package.

"Most chipmakers have found that for current and future process nodes, independent optimization of process steps is insufficient. The entire litho process must be integrated and co-optimized for the best performance. Eclipse extends the capabilities of their hardware and helps them to produce chips with smaller geometries, "said Bert Koek, senior vice president, applications product group at ASML. "With detailed knowledge of our scanner characteristics and interfaces we can work closely with our customers to integrate computational lithography solutions during R&D, and implement customized improvement targets during manufacturing."

Customers who have adopted Eclipse are seeing the results. STMicroelectronics, for example, will incorporate Eclipse in conjunction with a TWINSCAN NXT:1950i scanner for their 28-nanometer (nm) node. The key deliverables of the package are on-product specifications for both overlay and critical dimension uniformity (CDU). The 28 nm Eclipse package for ST includes a full range of products from ASML, including scanner tuning products, immersion scanner application, stabilization and conditioning as well as the ASML applications support to achieve the specified targets. Preparations for Eclipse at the next node have started with a feasibility study on 20 nm critical layer printing options.

"To optimize development cycle times and manufacturing solutions for 28 nm and beyond, ST is working closely with ASML to define targets, processes and design parameters," said Joel Hartmann, Technology R&D Group VP and general manager, Advanced CMOS, Derivatives and eNVM technology, STMicroelectronics, at Crolles, France. "ASML's Eclipse packages include application products, custom project deliverables and application support that enable joint process optimization."

About ASML

About holistic lithography and Eclipse