Press release - Veldhoven, the Netherlands, September 19, 2011

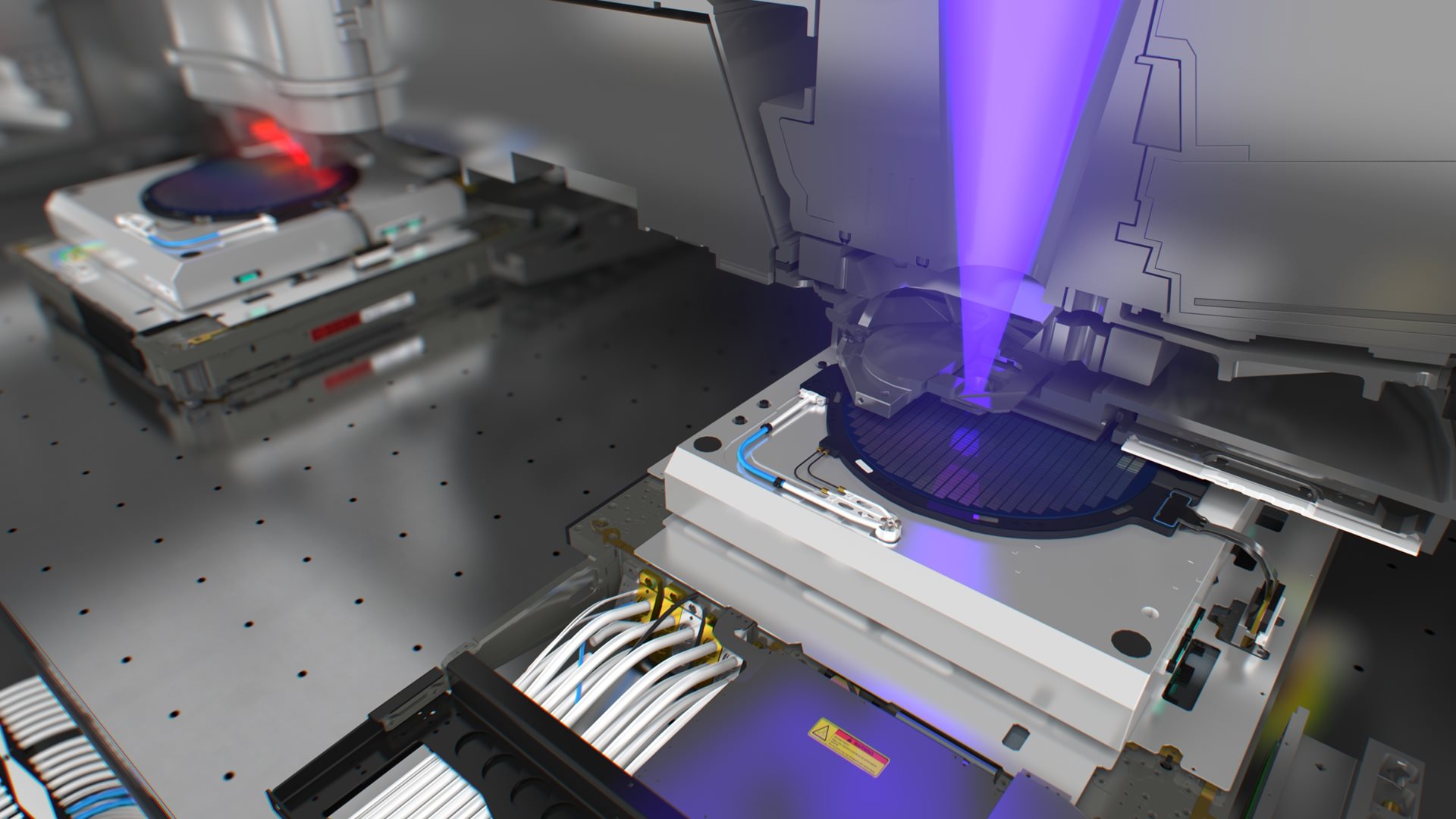

Brion Technologies, a division of ASML, today announced a new product for its popular Tachyon computational lithography platform. Tachyon MB-SRAF (model-based sub-resolution assist features) enables the high-speed, full-chip processing of advanced chip designs with larger process windows, greater productivity, and lower development costs than rule-based alternatives.

As chip geometries shrink to ever-smaller sizes, the ability to image the design properly depends on resolution enhancement techniques (RET) such as sub-resolution assist features which are not part of the original design. These assist features do not print, but aid in the proper imaging of the intended pattern. The application of SRAFs provides a larger process window, giving greater latitude in imaging and resulting in higher yielding devices.

With devices scaling down to the 2x nm nodes, the traditional rule-based approach for SRAF placement and sizing is fast becoming prohibitively complex, especially for two dimensional layers such as contacts, vias and metals. The industry-wide adoption of freeform illumination enabled by ASML’s FlexRay technology and Brion’s Tachyon SMO (source mask optimization) software further challenges the limitations of rule-based SRAF technology. To realize the substantial benefits in imaging made possible by the FlexRay illuminator, and at the same time make the solution robust against all pattern proximities and layout variations, there is an explosion in the necessary number of rules governing SRAF shape, size and placement. Development times for rule-based SRAFs are thus increasing dramatically and require many iterations of mask tape-out and wafer print tests. By contrast, a high quality and robust Tachyon MB-SRAF recipe can be developed and optimized in a fraction of this time and cost, in much the same way that model-based OPC has proven superior to rule-based OPC.

Model-based SRAF techniques have been in development for some time but until now have not been used for full-chip applications due to heavy compute costs, poor quality of correction, and/or the extreme impact to mask costs from the pixelated geometries they generate. Tachyon MB-SRAF has overcome these barriers and offers comprehensive design space coverage with embedded conflict resolution, mask rule check (MRC) compliance and SRAF printability prediction for full-chip implementation. In particular, compute times for Tachyon MB-SRAF have been substantially reduced to enable cost-effective full-chip processing, and are typically comparable with the corresponding OPC compute times on the same layer. Tachyon MB-SRAF has proven to be a key process window enabler for chipmakers who are developing and producing designs at 2x nm and below.

Sungwoo Ko, a senior research staff member at Hynix, recognized from his recent work with Tachyon MB-SRAF, “Having access to model-based SRAF capability from Brion Technologies has accelerated our learning and ability to deliver leading edge DRAM.”

“Freeform source mask optimization and full chip MB-SRAF are becoming essential for patterning 2D layers in next generation processes at the 2x nm nodes and beyond,” said Jim Koonmen, general manager of Brion. “Our Tachyon MB-SRAF is the first in the industry that has been proven at multiple customer sites worldwide in both logic and memory full-chip applications. It delivers a cost effective solution and enables our customers to tape-out their advanced masks on time and with excellent results.”

About ASML

About Brion Technologies